sysinfo.h File Reference

#include <stdio.h>#include <stdlib.h>#include <string.h>#include <winpr/winpr.h>#include <winpr/wtypes.h>Data Structures | |

| struct | SYSTEM_INFO |

Typedefs | |

| typedef struct SYSTEM_INFO * | LPSYSTEM_INFO |

Functions | |

| WINPR_API void | GetSystemInfo (LPSYSTEM_INFO lpSystemInfo) |

| WINPR_API void | GetNativeSystemInfo (LPSYSTEM_INFO lpSystemInfo) |

| WINPR_API void | GetSystemTime (LPSYSTEMTIME lpSystemTime) |

| WINPR_API BOOL | SetSystemTime (CONST SYSTEMTIME *lpSystemTime) |

| WINPR_API VOID | GetLocalTime (LPSYSTEMTIME lpSystemTime) |

| WINPR_API BOOL | SetLocalTime (CONST SYSTEMTIME *lpSystemTime) |

| WINPR_API VOID | GetSystemTimeAsFileTime (LPFILETIME lpSystemTimeAsFileTime) |

| WINPR_API BOOL | GetSystemTimeAdjustment (PDWORD lpTimeAdjustment, PDWORD lpTimeIncrement, PBOOL lpTimeAdjustmentDisabled) |

| WINPR_API BOOL | IsProcessorFeaturePresent (DWORD ProcessorFeature) |

| WINPR_API DWORD | GetTickCount (void) |

| WINPR_API BOOL | GetComputerNameA (LPSTR lpBuffer, LPDWORD lpnSize) |

| WINPR_API BOOL | GetComputerNameW (LPWSTR lpBuffer, LPDWORD lpnSize) |

| WINPR_API BOOL | GetComputerNameExA (COMPUTER_NAME_FORMAT NameType, LPSTR lpBuffer, LPDWORD lpnSize) |

| WINPR_API BOOL | GetComputerNameExW (COMPUTER_NAME_FORMAT NameType, LPWSTR lpBuffer, LPDWORD lpnSize) |

| WINPR_API ULONGLONG | winpr_GetTickCount64 (void) |

| WINPR_API UINT64 | winpr_GetTickCount64NS (void) |

| WINPR_API UINT64 | winpr_GetUnixTimeNS (void) |

| WINPR_API DWORD | GetTickCountPrecise (void) |

| WINPR_API BOOL | IsProcessorFeaturePresentEx (DWORD ProcessorFeature) |

Macro Definition Documentation

◆ GetComputerName

| #define GetComputerName GetComputerNameA |

◆ GetComputerNameEx

| #define GetComputerNameEx GetComputerNameExA |

◆ GetTickCount64

| #define GetTickCount64 winpr_GetTickCount64 |

◆ MAX_COMPUTERNAME_LENGTH

| #define MAX_COMPUTERNAME_LENGTH 31 |

◆ PF_3DNOW_INSTRUCTIONS_AVAILABLE

| #define PF_3DNOW_INSTRUCTIONS_AVAILABLE 7 |

◆ PF_ARM_64BIT_LOADSTORE_ATOMIC

| #define PF_ARM_64BIT_LOADSTORE_ATOMIC 25 |

◆ PF_ARM_CACHE_CAN_BE_LOCKED_DOWN

| #define PF_ARM_CACHE_CAN_BE_LOCKED_DOWN 0x80000015 |

◆ PF_ARM_DIVIDE_INSTRUCTION_AVAILABLE

| #define PF_ARM_DIVIDE_INSTRUCTION_AVAILABLE 24 |

◆ PF_ARM_DSP

| #define PF_ARM_DSP 0x80000007 |

◆ PF_ARM_DTCM

| #define PF_ARM_DTCM 0x80000012 |

◆ PF_ARM_EXTERNAL_CACHE_AVAILABLE

| #define PF_ARM_EXTERNAL_CACHE_AVAILABLE 26 |

◆ PF_ARM_FMAC_INSTRUCTIONS_AVAILABLE

| #define PF_ARM_FMAC_INSTRUCTIONS_AVAILABLE 27 |

◆ PF_ARM_INTEL_PMU

| #define PF_ARM_INTEL_PMU 0x80010002 |

◆ PF_ARM_INTEL_WMMX

| #define PF_ARM_INTEL_WMMX 0x80010003 |

◆ PF_ARM_INTEL_XSCALE

| #define PF_ARM_INTEL_XSCALE 0x80010001 |

◆ PF_ARM_ITCM

| #define PF_ARM_ITCM 0x80000011 |

◆ PF_ARM_JAZELLE

| #define PF_ARM_JAZELLE 0x80000006 |

◆ PF_ARM_L2CACHE

| #define PF_ARM_L2CACHE 0x8000000D |

◆ PF_ARM_L2CACHE_COPROC

| #define PF_ARM_L2CACHE_COPROC 0x80000017 |

◆ PF_ARM_L2CACHE_MEMORY_MAPPED

| #define PF_ARM_L2CACHE_MEMORY_MAPPED 0x80000016 |

◆ PF_ARM_MBX

| #define PF_ARM_MBX 0x8000000C |

◆ PF_ARM_MOVE_CP

| #define PF_ARM_MOVE_CP 0x80000008 |

◆ PF_ARM_MPU

| #define PF_ARM_MPU 0x8000000A |

◆ PF_ARM_NEON

| #define PF_ARM_NEON 0x8000001B |

◆ PF_ARM_NEON_INSTRUCTIONS_AVAILABLE

| #define PF_ARM_NEON_INSTRUCTIONS_AVAILABLE 19 |

◆ PF_ARM_PHYSICALLY_TAGGED_CACHE

| #define PF_ARM_PHYSICALLY_TAGGED_CACHE 0x8000000E |

◆ PF_ARM_T2EE

| #define PF_ARM_T2EE 0x80000019 |

◆ PF_ARM_THUMB

| #define PF_ARM_THUMB 0x80000005 |

◆ PF_ARM_THUMB2

| #define PF_ARM_THUMB2 0x80000018 |

◆ PF_ARM_UNALIGNED_ACCESS

| #define PF_ARM_UNALIGNED_ACCESS 0x8000001C |

◆ PF_ARM_UNIFIED_CACHE

| #define PF_ARM_UNIFIED_CACHE 0x80000013 |

◆ PF_ARM_V4

| #define PF_ARM_V4 0x80000001 |

◆ PF_ARM_V5

| #define PF_ARM_V5 0x80000002 |

◆ PF_ARM_V6

| #define PF_ARM_V6 0x80000003 |

◆ PF_ARM_V7

| #define PF_ARM_V7 0x80000004 |

◆ PF_ARM_V81_ATOMIC_INSTRUCTIONS_AVAILABLE

| #define PF_ARM_V81_ATOMIC_INSTRUCTIONS_AVAILABLE 34 |

◆ PF_ARM_V82_DP_INSTRUCTIONS_AVAILABLE

| #define PF_ARM_V82_DP_INSTRUCTIONS_AVAILABLE 43 |

◆ PF_ARM_V83_JSCVT_INSTRUCTIONS_AVAILABLE

| #define PF_ARM_V83_JSCVT_INSTRUCTIONS_AVAILABLE 44 |

◆ PF_ARM_V83_LRCPC_INSTRUCTIONS_AVAILABLE

| #define PF_ARM_V83_LRCPC_INSTRUCTIONS_AVAILABLE 45 |

◆ PF_ARM_V8_CRC32_INSTRUCTIONS_AVAILABLE

| #define PF_ARM_V8_CRC32_INSTRUCTIONS_AVAILABLE 31 |

◆ PF_ARM_V8_CRYPTO_INSTRUCTIONS_AVAILABLE

| #define PF_ARM_V8_CRYPTO_INSTRUCTIONS_AVAILABLE 30 |

◆ PF_ARM_V8_INSTRUCTIONS_AVAILABLE

| #define PF_ARM_V8_INSTRUCTIONS_AVAILABLE 29 |

◆ PF_ARM_VFP10

| #define PF_ARM_VFP10 0x80000009 |

◆ PF_ARM_VFP3

| #define PF_ARM_VFP3 0x8000001A |

◆ PF_ARM_VFP_32_REGISTERS_AVAILABLE

| #define PF_ARM_VFP_32_REGISTERS_AVAILABLE 18 |

◆ PF_ARM_VFP_DOUBLE_PRECISION

| #define PF_ARM_VFP_DOUBLE_PRECISION 0x80000010 |

◆ PF_ARM_VFP_SINGLE_PRECISION

| #define PF_ARM_VFP_SINGLE_PRECISION 0x8000000F |

◆ PF_ARM_WRITE_BACK_CACHE

| #define PF_ARM_WRITE_BACK_CACHE 0x80000014 |

◆ PF_ARM_WRITE_BUFFER

| #define PF_ARM_WRITE_BUFFER 0x8000000B |

◆ PF_AVX2_INSTRUCTIONS_AVAILABLE

| #define PF_AVX2_INSTRUCTIONS_AVAILABLE 40 |

◆ PF_AVX512F_INSTRUCTIONS_AVAILABLE

| #define PF_AVX512F_INSTRUCTIONS_AVAILABLE 41 |

◆ PF_AVX_INSTRUCTIONS_AVAILABLE

| #define PF_AVX_INSTRUCTIONS_AVAILABLE 39 |

◆ PF_CHANNELS_ENABLED

| #define PF_CHANNELS_ENABLED 16 |

◆ PF_COMPARE64_EXCHANGE128

| #define PF_COMPARE64_EXCHANGE128 15 |

◆ PF_COMPARE_EXCHANGE128

| #define PF_COMPARE_EXCHANGE128 14 |

◆ PF_COMPARE_EXCHANGE_DOUBLE

| #define PF_COMPARE_EXCHANGE_DOUBLE 2 |

◆ PF_EX_3DNOW_PREFETCH

| #define PF_EX_3DNOW_PREFETCH 2 |

◆ PF_EX_ARM_IDIVA

| #define PF_EX_ARM_IDIVA 13 |

◆ PF_EX_ARM_IDIVT

| #define PF_EX_ARM_IDIVT 14 |

◆ PF_EX_ARM_VFP1

| #define PF_EX_ARM_VFP1 10 |

◆ PF_EX_ARM_VFP3D16

| #define PF_EX_ARM_VFP3D16 11 |

◆ PF_EX_ARM_VFP4

| #define PF_EX_ARM_VFP4 12 |

◆ PF_EX_AVX

| #define PF_EX_AVX 6 |

◆ PF_EX_AVX2

| #define PF_EX_AVX2 9 |

◆ PF_EX_AVX512F

| #define PF_EX_AVX512F 16 |

◆ PF_EX_AVX_AES

| #define PF_EX_AVX_AES 8 |

◆ PF_EX_AVX_PCLMULQDQ

| #define PF_EX_AVX_PCLMULQDQ 15 |

◆ PF_EX_FMA

| #define PF_EX_FMA 7 |

◆ PF_EX_LZCNT

| #define PF_EX_LZCNT 1 |

◆ PF_EX_SSE41

| #define PF_EX_SSE41 4 |

◆ PF_EX_SSE42

| #define PF_EX_SSE42 5 |

◆ PF_EX_SSSE3

| #define PF_EX_SSSE3 3 |

◆ PF_FASTFAIL_AVAILABLE

| #define PF_FASTFAIL_AVAILABLE 23 |

◆ PF_FLOATING_POINT_EMULATED

| #define PF_FLOATING_POINT_EMULATED 1 |

◆ PF_FLOATING_POINT_PRECISION_ERRATA

| #define PF_FLOATING_POINT_PRECISION_ERRATA 0 |

◆ PF_MMX_INSTRUCTIONS_AVAILABLE

| #define PF_MMX_INSTRUCTIONS_AVAILABLE 3 |

◆ PF_NX_ENABLED

| #define PF_NX_ENABLED 12 |

◆ PF_PAE_ENABLED

| #define PF_PAE_ENABLED 9 |

◆ PF_PPC_MOVEMEM_64BIT_OK

| #define PF_PPC_MOVEMEM_64BIT_OK 4 |

◆ PF_RDTSC_INSTRUCTION_AVAILABLE

| #define PF_RDTSC_INSTRUCTION_AVAILABLE 8 |

◆ PF_RDWRFSGSBASE_AVAILABLE

| #define PF_RDWRFSGSBASE_AVAILABLE 22 |

◆ PF_SECOND_LEVEL_ADDRESS_TRANSLATION

| #define PF_SECOND_LEVEL_ADDRESS_TRANSLATION 20 |

◆ PF_SSE2_INSTRUCTIONS_AVAILABLE

| #define PF_SSE2_INSTRUCTIONS_AVAILABLE PF_XMMI64_INSTRUCTIONS_AVAILABLE |

◆ PF_SSE3_INSTRUCTIONS_AVAILABLE

| #define PF_SSE3_INSTRUCTIONS_AVAILABLE 13 |

◆ PF_SSE4_1_INSTRUCTIONS_AVAILABLE

| #define PF_SSE4_1_INSTRUCTIONS_AVAILABLE 37 |

◆ PF_SSE4_2_INSTRUCTIONS_AVAILABLE

| #define PF_SSE4_2_INSTRUCTIONS_AVAILABLE 38 |

◆ PF_SSE_DAZ_MODE_AVAILABLE

| #define PF_SSE_DAZ_MODE_AVAILABLE 11 |

◆ PF_SSE_INSTRUCTIONS_AVAILABLE

| #define PF_SSE_INSTRUCTIONS_AVAILABLE PF_XMMI_INSTRUCTIONS_AVAILABLE |

◆ PF_SSSE3_INSTRUCTIONS_AVAILABLE

| #define PF_SSSE3_INSTRUCTIONS_AVAILABLE 36 |

◆ PF_VIRT_FIRMWARE_ENABLED

| #define PF_VIRT_FIRMWARE_ENABLED 21 |

◆ PF_XMMI64_INSTRUCTIONS_AVAILABLE

| #define PF_XMMI64_INSTRUCTIONS_AVAILABLE 10 /* SSE2 */ |

◆ PF_XMMI_INSTRUCTIONS_AVAILABLE

| #define PF_XMMI_INSTRUCTIONS_AVAILABLE 6 /* SSE */ |

◆ PF_XSAVE_ENABLED

| #define PF_XSAVE_ENABLED 17 |

◆ PROCESSOR_ALPHA_21064

| #define PROCESSOR_ALPHA_21064 21064 |

◆ PROCESSOR_AMD_X8664

| #define PROCESSOR_AMD_X8664 8664 |

◆ PROCESSOR_ARCHITECTURE_ALPHA

| #define PROCESSOR_ARCHITECTURE_ALPHA 2 |

◆ PROCESSOR_ARCHITECTURE_ALPHA64

| #define PROCESSOR_ARCHITECTURE_ALPHA64 7 |

◆ PROCESSOR_ARCHITECTURE_AMD64

| #define PROCESSOR_ARCHITECTURE_AMD64 9 |

◆ PROCESSOR_ARCHITECTURE_ARM

| #define PROCESSOR_ARCHITECTURE_ARM 5 |

◆ PROCESSOR_ARCHITECTURE_ARM64

| #define PROCESSOR_ARCHITECTURE_ARM64 12 |

◆ PROCESSOR_ARCHITECTURE_E2K

| #define PROCESSOR_ARCHITECTURE_E2K 14 |

◆ PROCESSOR_ARCHITECTURE_IA32_ON_WIN64

| #define PROCESSOR_ARCHITECTURE_IA32_ON_WIN64 10 |

◆ PROCESSOR_ARCHITECTURE_IA64

| #define PROCESSOR_ARCHITECTURE_IA64 6 |

◆ PROCESSOR_ARCHITECTURE_INTEL

| #define PROCESSOR_ARCHITECTURE_INTEL 0 |

WinPR: Windows Portable Runtime System Information

Copyright 2012 Marc-Andre Moreau marcandre.moreau@gmail.com

Licensed under the Apache License, Version 2.0 (the "License"); you may not use this file except in compliance with the License. You may obtain a copy of the License at

http://www.apache.org/licenses/LICENSE-2.0

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

◆ PROCESSOR_ARCHITECTURE_MIPS

| #define PROCESSOR_ARCHITECTURE_MIPS 1 |

◆ PROCESSOR_ARCHITECTURE_MIPS64

| #define PROCESSOR_ARCHITECTURE_MIPS64 13 |

◆ PROCESSOR_ARCHITECTURE_MSIL

| #define PROCESSOR_ARCHITECTURE_MSIL 8 |

◆ PROCESSOR_ARCHITECTURE_NEUTRAL

| #define PROCESSOR_ARCHITECTURE_NEUTRAL 11 |

◆ PROCESSOR_ARCHITECTURE_PPC

| #define PROCESSOR_ARCHITECTURE_PPC 3 |

◆ PROCESSOR_ARCHITECTURE_SHX

| #define PROCESSOR_ARCHITECTURE_SHX 4 |

◆ PROCESSOR_ARCHITECTURE_UNKNOWN

| #define PROCESSOR_ARCHITECTURE_UNKNOWN 0xFFFF |

◆ PROCESSOR_ARM720

| #define PROCESSOR_ARM720 1824 |

◆ PROCESSOR_ARM820

| #define PROCESSOR_ARM820 2080 |

◆ PROCESSOR_ARM920

| #define PROCESSOR_ARM920 2336 |

◆ PROCESSOR_ARM_7TDMI

| #define PROCESSOR_ARM_7TDMI 70001 |

◆ PROCESSOR_HITACHI_SH3

| #define PROCESSOR_HITACHI_SH3 10003 |

◆ PROCESSOR_HITACHI_SH3E

| #define PROCESSOR_HITACHI_SH3E 10004 |

◆ PROCESSOR_HITACHI_SH4

| #define PROCESSOR_HITACHI_SH4 10005 |

◆ PROCESSOR_INTEL_386

| #define PROCESSOR_INTEL_386 386 |

◆ PROCESSOR_INTEL_486

| #define PROCESSOR_INTEL_486 486 |

◆ PROCESSOR_INTEL_IA64

| #define PROCESSOR_INTEL_IA64 2200 |

◆ PROCESSOR_INTEL_PENTIUM

| #define PROCESSOR_INTEL_PENTIUM 586 |

◆ PROCESSOR_MIPS_R4000

| #define PROCESSOR_MIPS_R4000 4000 |

◆ PROCESSOR_MOTOROLA_821

| #define PROCESSOR_MOTOROLA_821 821 |

◆ PROCESSOR_OPTIL

| #define PROCESSOR_OPTIL 0x494F |

◆ PROCESSOR_PPC_601

| #define PROCESSOR_PPC_601 601 |

◆ PROCESSOR_PPC_603

| #define PROCESSOR_PPC_603 603 |

◆ PROCESSOR_PPC_604

| #define PROCESSOR_PPC_604 604 |

◆ PROCESSOR_PPC_620

| #define PROCESSOR_PPC_620 620 |

◆ PROCESSOR_SHx_SH3

| #define PROCESSOR_SHx_SH3 103 |

◆ PROCESSOR_SHx_SH4

| #define PROCESSOR_SHx_SH4 104 |

◆ PROCESSOR_STRONGARM

| #define PROCESSOR_STRONGARM 2577 |

◆ VER_NT_DOMAIN_CONTROLLER

| #define VER_NT_DOMAIN_CONTROLLER 0x0000002 |

◆ VER_NT_SERVER

| #define VER_NT_SERVER 0x0000003 |

◆ VER_NT_WORKSTATION

| #define VER_NT_WORKSTATION 0x0000001 |

◆ WINPR_TIME_NS_REM_MS

| #define WINPR_TIME_NS_REM_MS | ( | ns | ) | (WINPR_TIME_NS_REM_US(ns) / 1000ull) |

◆ WINPR_TIME_NS_REM_NS

| #define WINPR_TIME_NS_REM_NS | ( | ns | ) | ((ns) % 1000000000ull) |

◆ WINPR_TIME_NS_REM_US

| #define WINPR_TIME_NS_REM_US | ( | ns | ) | (WINPR_TIME_NS_REM_NS(ns) / 1000ull) |

◆ WINPR_TIME_NS_TO_MS

| #define WINPR_TIME_NS_TO_MS | ( | ns | ) | ((ns) / 1000000ull) |

◆ WINPR_TIME_NS_TO_S

| #define WINPR_TIME_NS_TO_S | ( | ns | ) | ((ns) / 1000000000ull) |

◆ WINPR_TIME_NS_TO_US

| #define WINPR_TIME_NS_TO_US | ( | ns | ) | ((ns) / 1000ull) |

Typedef Documentation

◆ LPSYSTEM_INFO

| typedef struct SYSTEM_INFO * LPSYSTEM_INFO |

Enumeration Type Documentation

◆ COMPUTER_NAME_FORMAT

| enum COMPUTER_NAME_FORMAT |

Function Documentation

◆ GetComputerNameA()

| WINPR_API BOOL GetComputerNameA | ( | LPSTR | lpBuffer, |

| LPDWORD | lpnSize | ||

| ) |

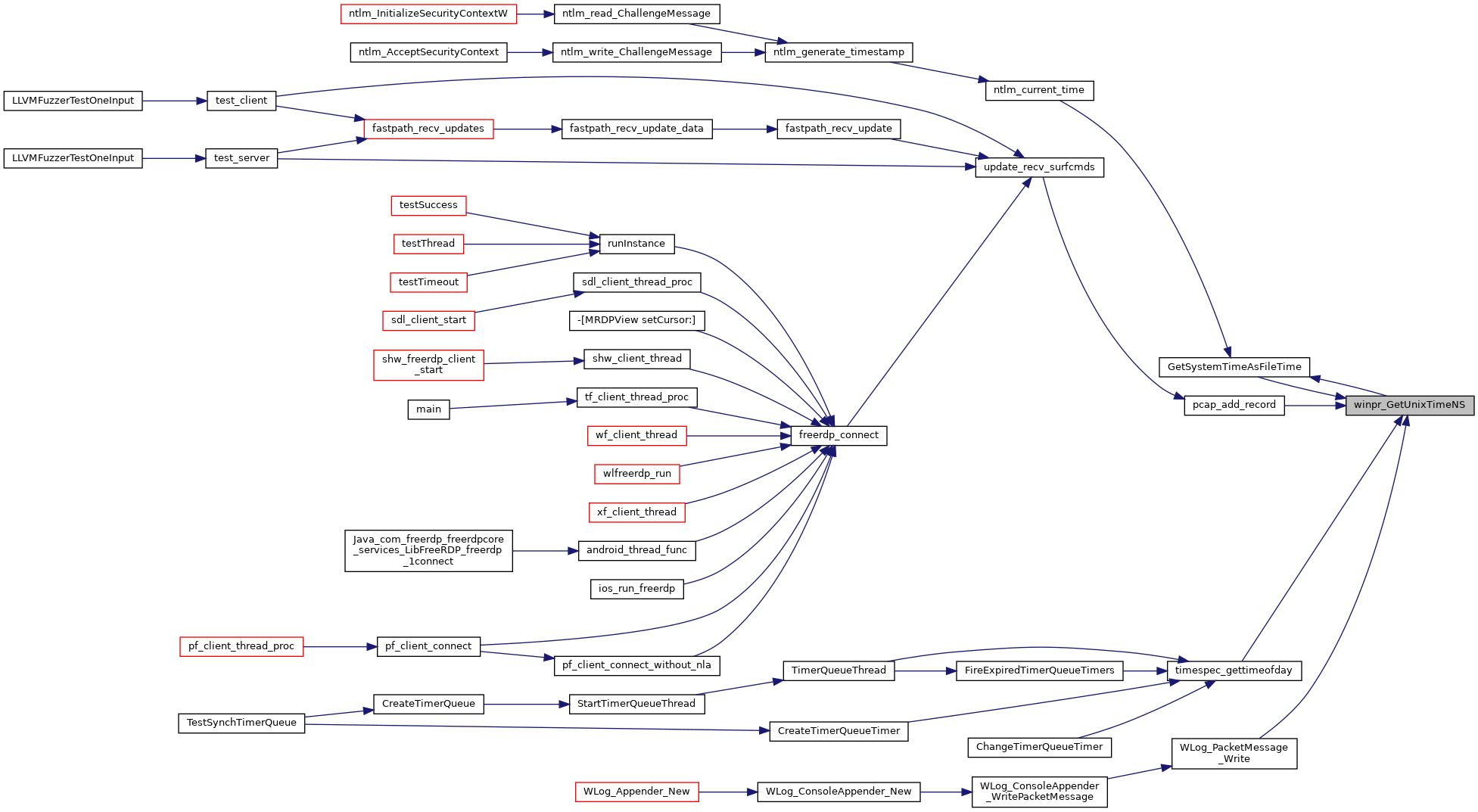

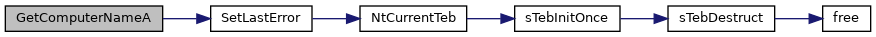

Here is the call graph for this function:

Here is the caller graph for this function:

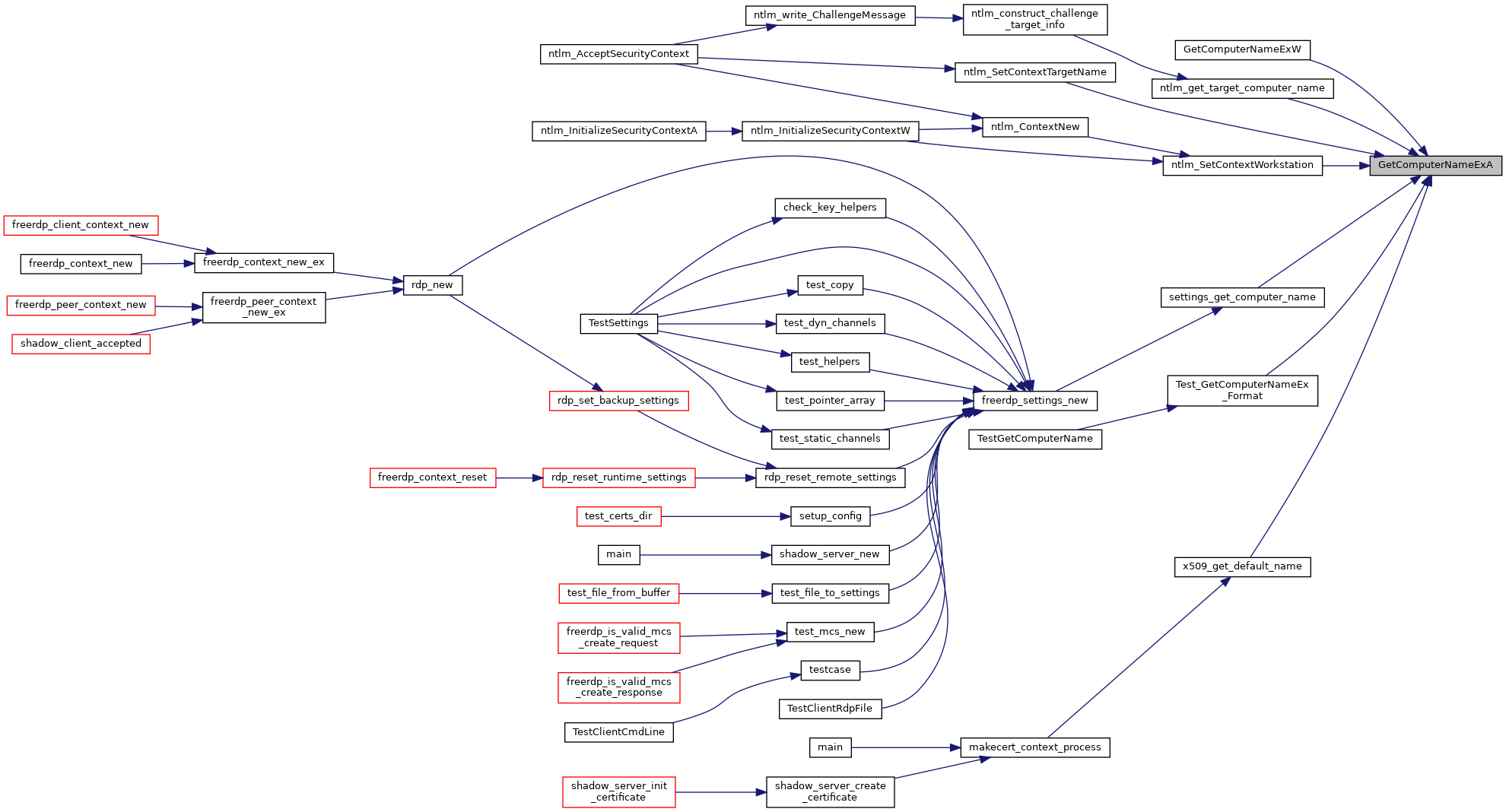

◆ GetComputerNameExA()

| WINPR_API BOOL GetComputerNameExA | ( | COMPUTER_NAME_FORMAT | NameType, |

| LPSTR | lpBuffer, | ||

| LPDWORD | lpnSize | ||

| ) |

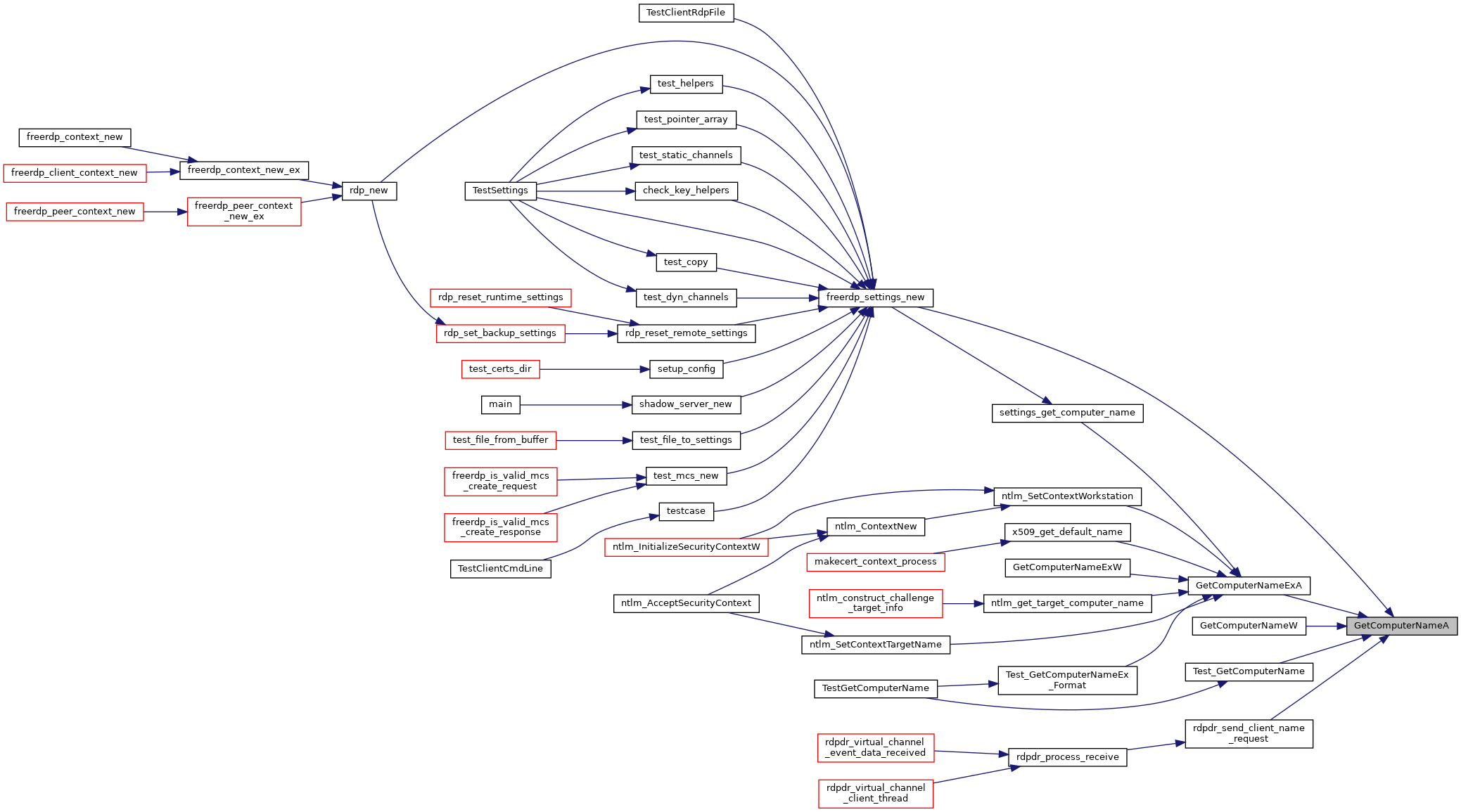

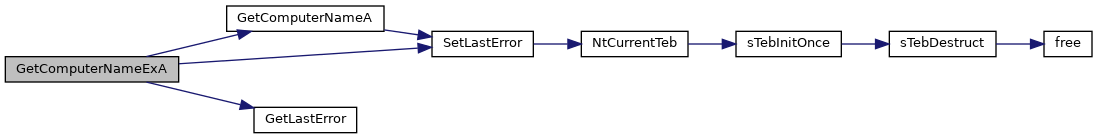

Here is the call graph for this function:

Here is the caller graph for this function:

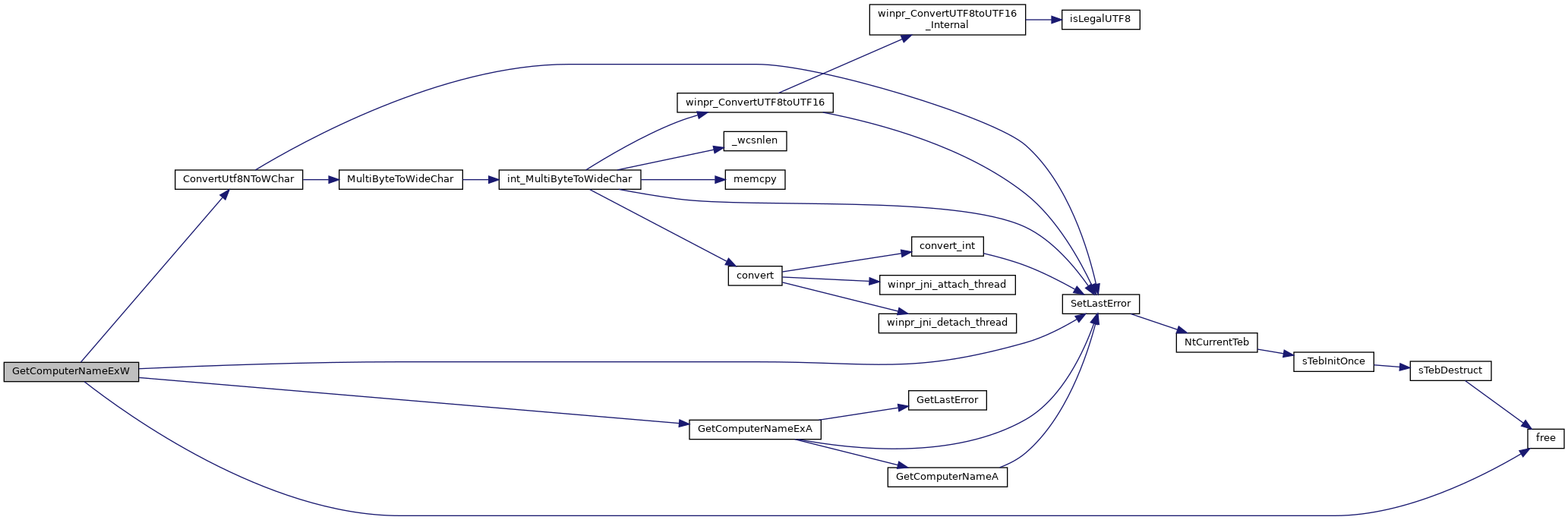

◆ GetComputerNameExW()

| WINPR_API BOOL GetComputerNameExW | ( | COMPUTER_NAME_FORMAT | NameType, |

| LPWSTR | lpBuffer, | ||

| LPDWORD | lpnSize | ||

| ) |

Here is the call graph for this function:

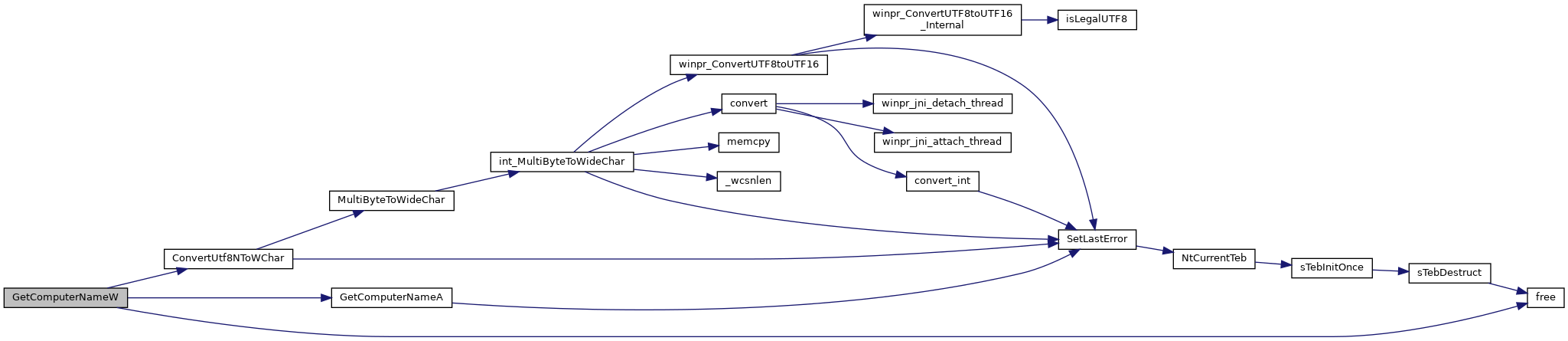

◆ GetComputerNameW()

| WINPR_API BOOL GetComputerNameW | ( | LPWSTR | lpBuffer, |

| LPDWORD | lpnSize | ||

| ) |

Here is the call graph for this function:

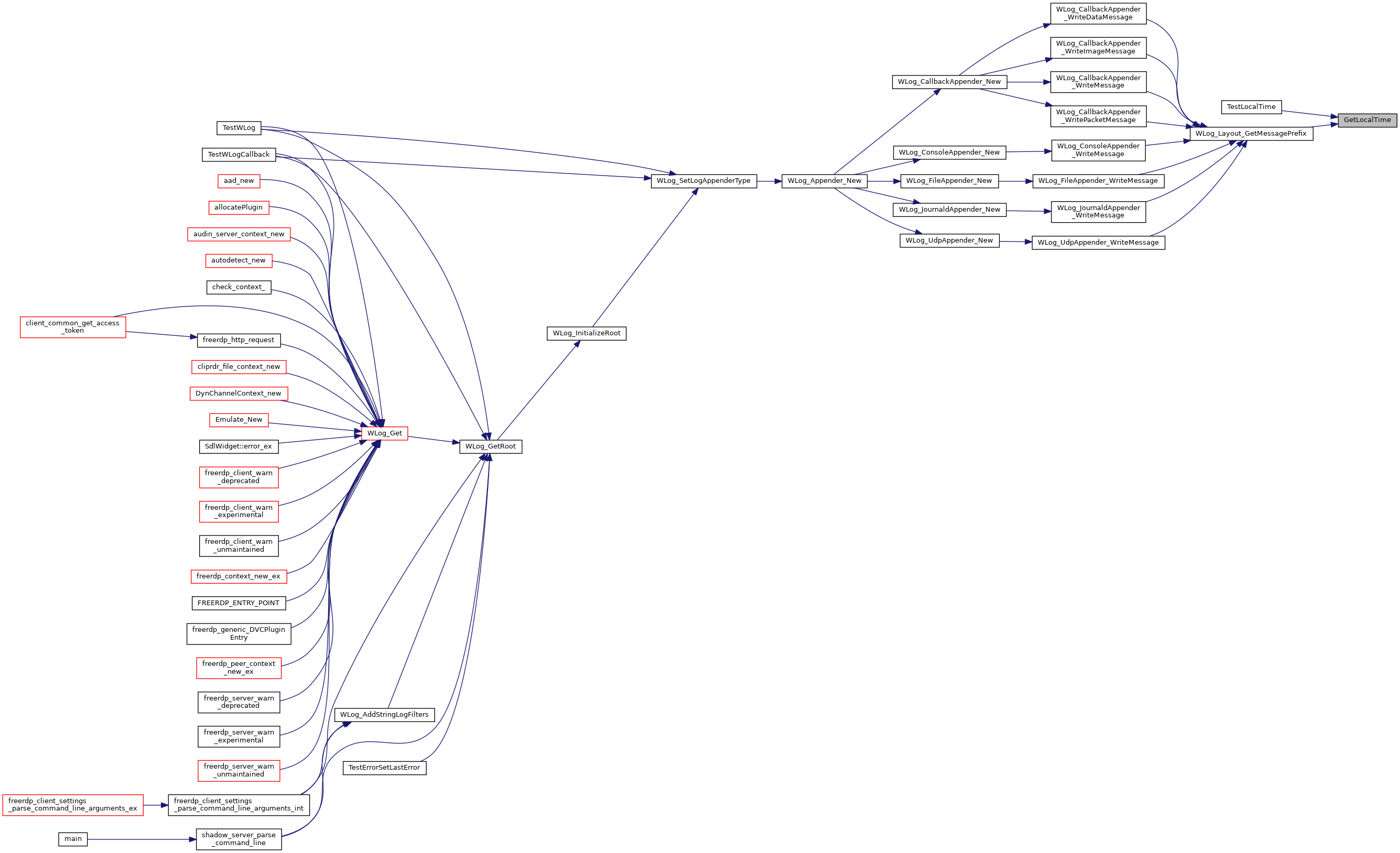

◆ GetLocalTime()

| WINPR_API VOID GetLocalTime | ( | LPSYSTEMTIME | lpSystemTime | ) |

Here is the call graph for this function:

Here is the caller graph for this function:

◆ GetNativeSystemInfo()

| WINPR_API void GetNativeSystemInfo | ( | LPSYSTEM_INFO | lpSystemInfo | ) |

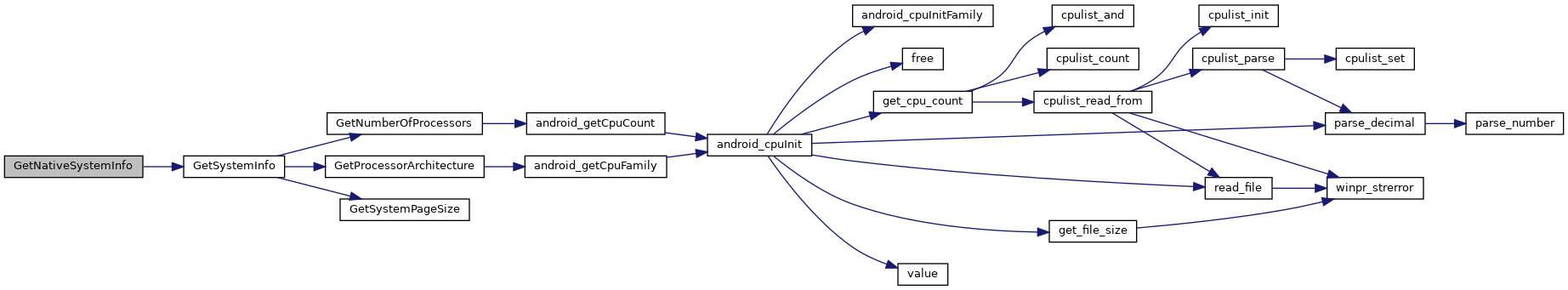

Here is the call graph for this function:

Here is the caller graph for this function:

◆ GetSystemInfo()

| WINPR_API void GetSystemInfo | ( | LPSYSTEM_INFO | lpSystemInfo | ) |

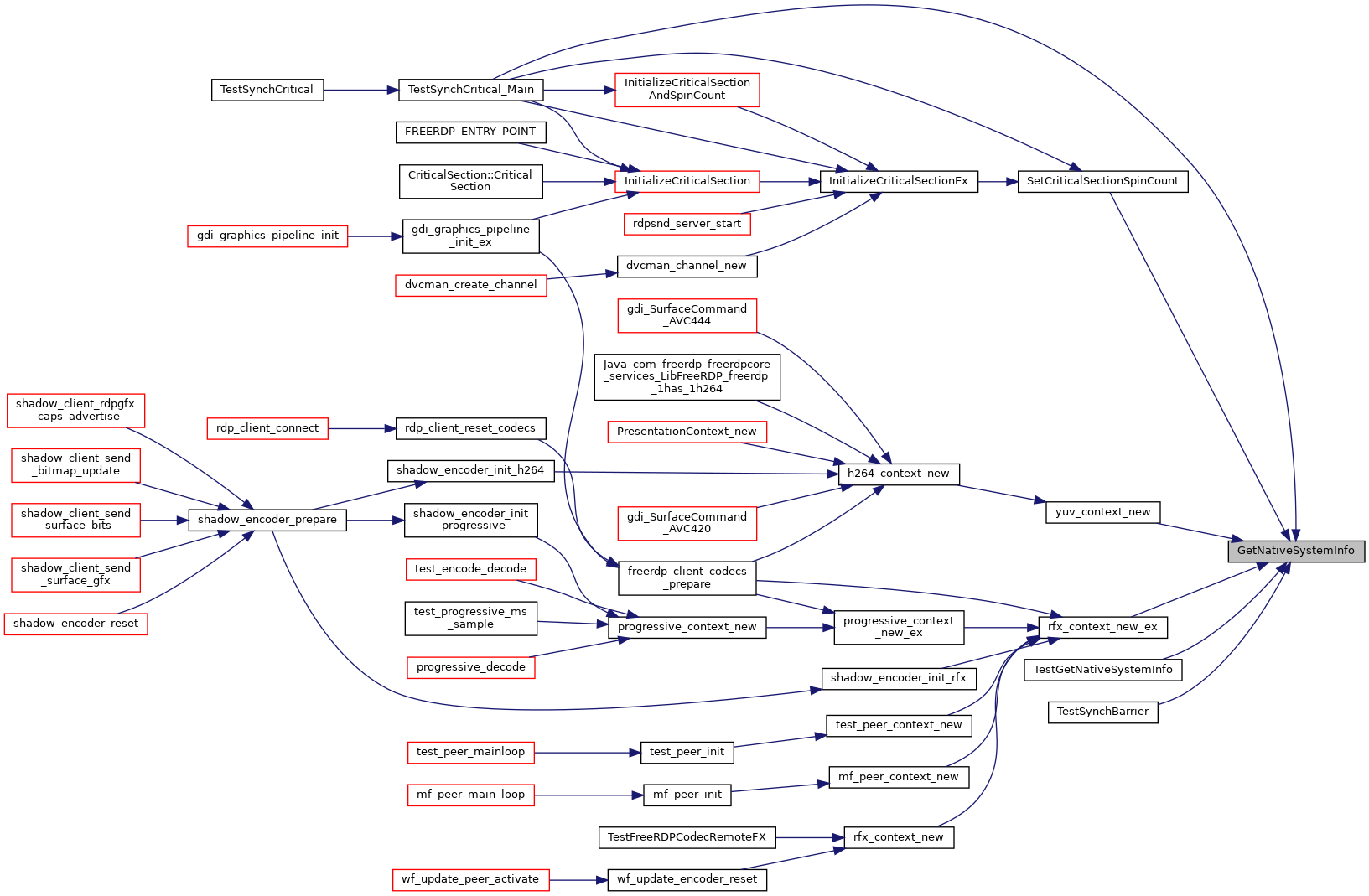

Here is the call graph for this function:

Here is the caller graph for this function:

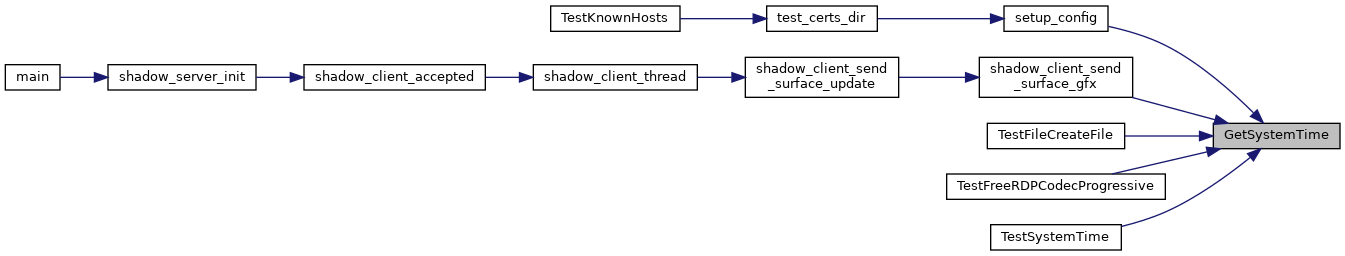

◆ GetSystemTime()

| WINPR_API void GetSystemTime | ( | LPSYSTEMTIME | lpSystemTime | ) |

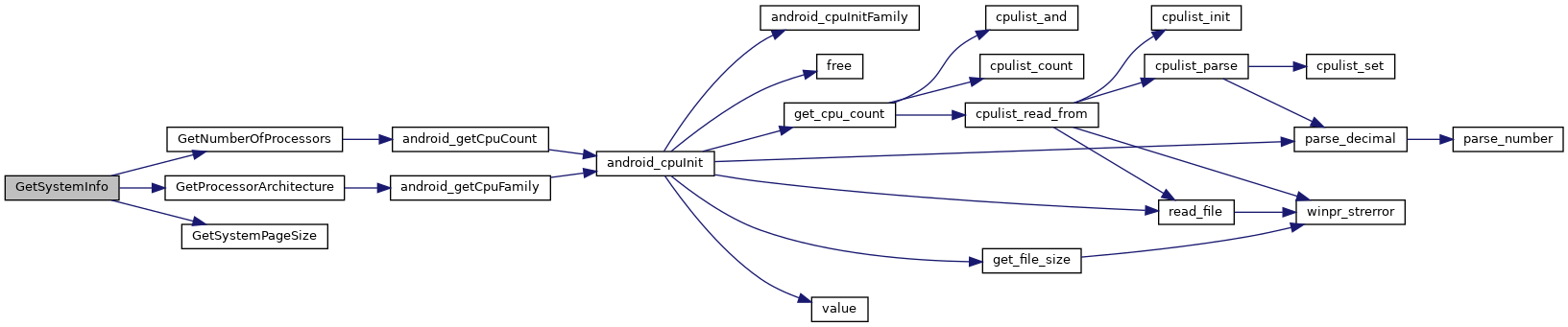

Here is the call graph for this function:

Here is the caller graph for this function:

◆ GetSystemTimeAdjustment()

| WINPR_API BOOL GetSystemTimeAdjustment | ( | PDWORD | lpTimeAdjustment, |

| PDWORD | lpTimeIncrement, | ||

| PBOOL | lpTimeAdjustmentDisabled | ||

| ) |

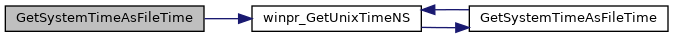

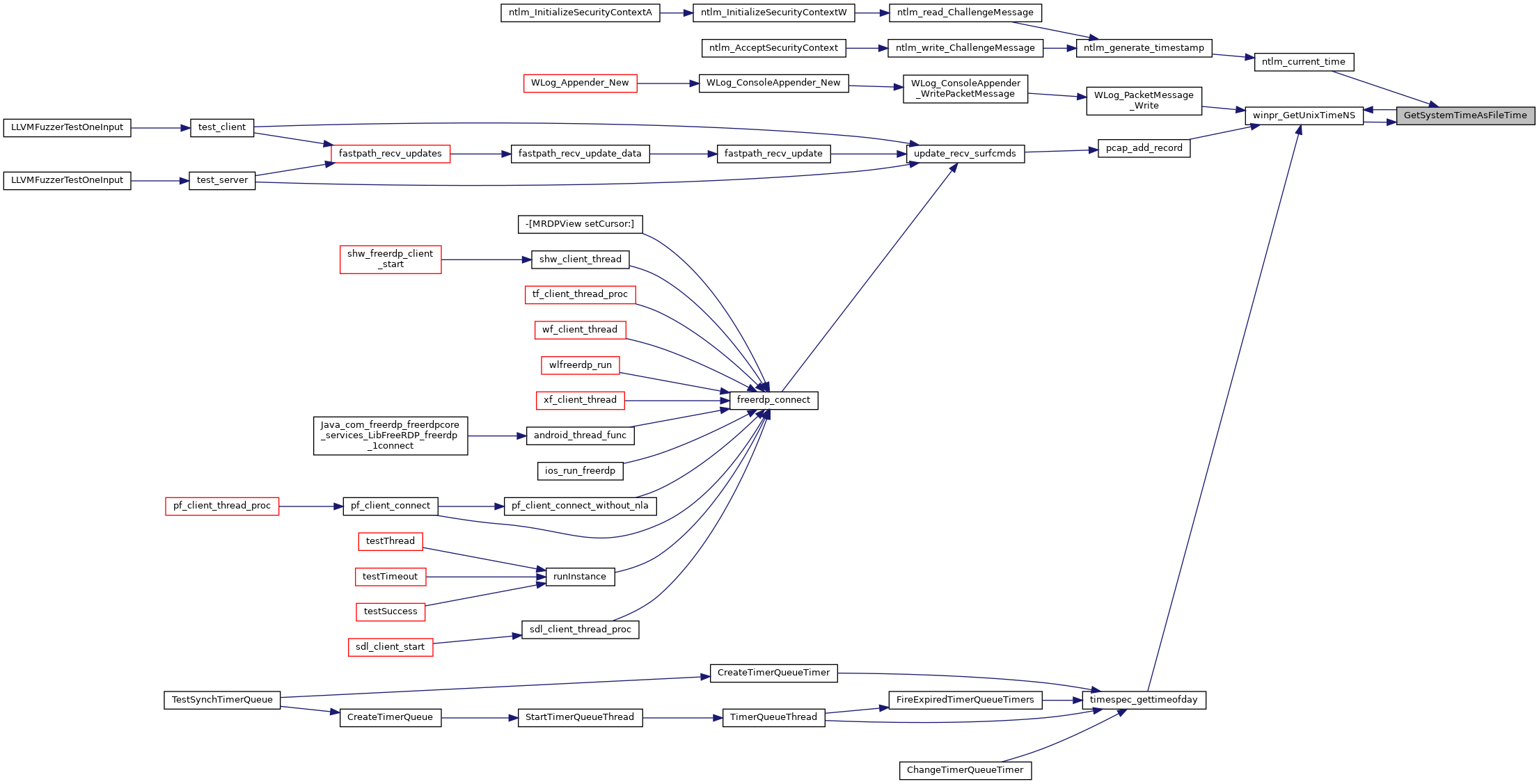

◆ GetSystemTimeAsFileTime()

| WINPR_API VOID GetSystemTimeAsFileTime | ( | LPFILETIME | lpSystemTimeAsFileTime | ) |

Here is the call graph for this function:

Here is the caller graph for this function:

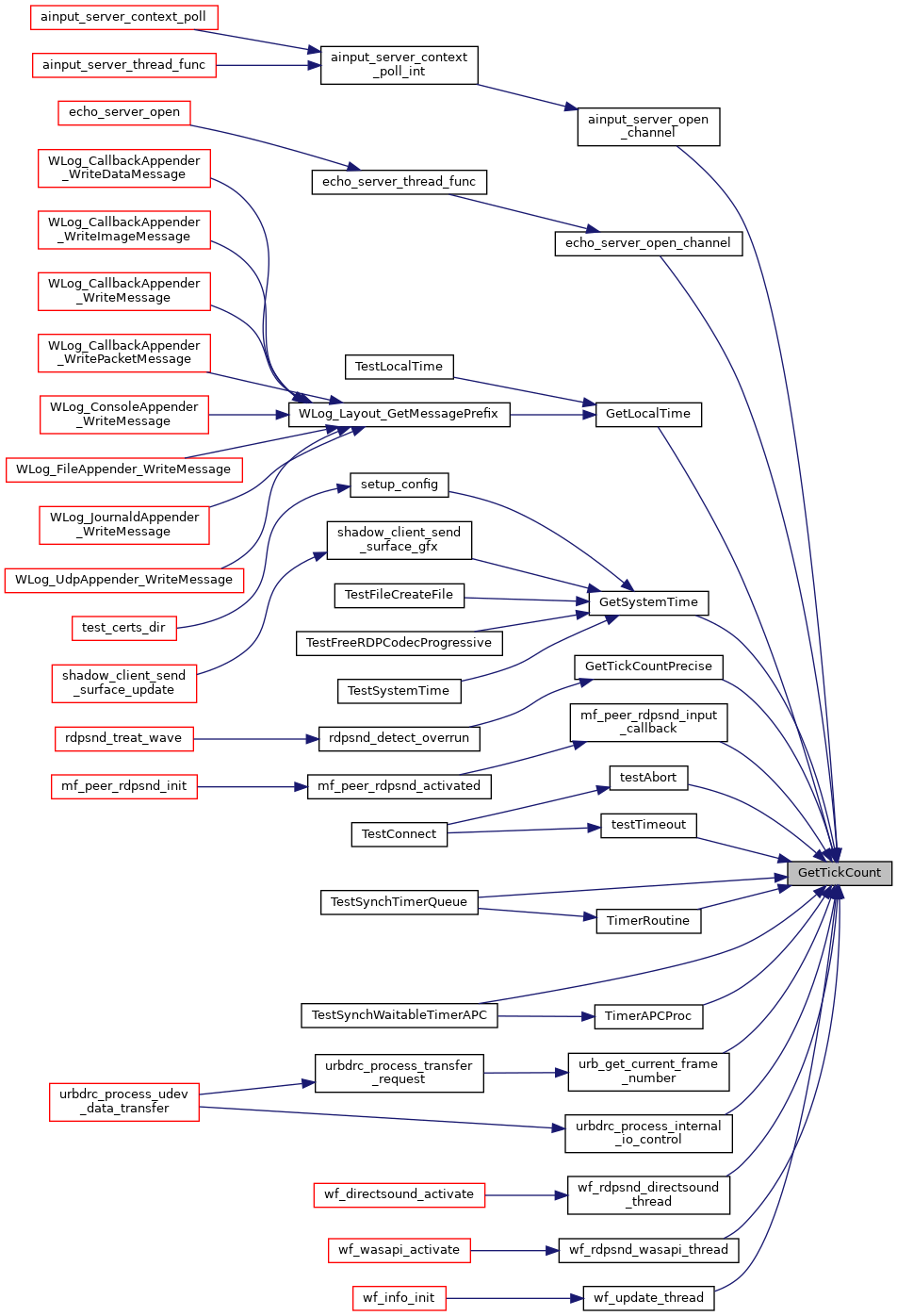

◆ GetTickCount()

| WINPR_API DWORD GetTickCount | ( | void | ) |

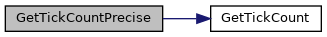

Here is the caller graph for this function:

◆ GetTickCountPrecise()

| WINPR_API DWORD GetTickCountPrecise | ( | void | ) |

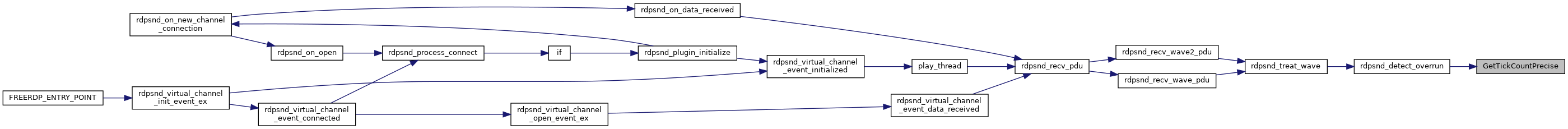

Here is the call graph for this function:

Here is the caller graph for this function:

◆ IsProcessorFeaturePresent()

| WINPR_API BOOL IsProcessorFeaturePresent | ( | DWORD | ProcessorFeature | ) |

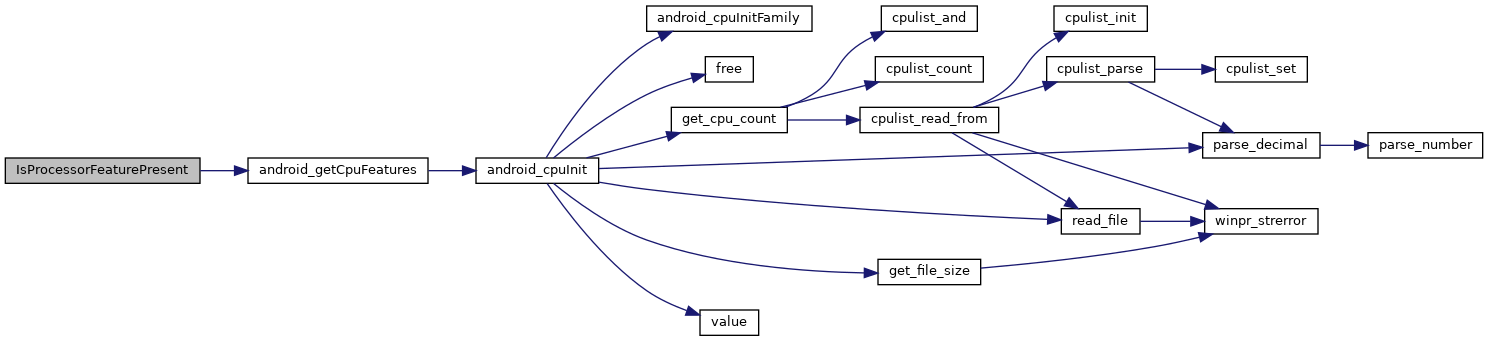

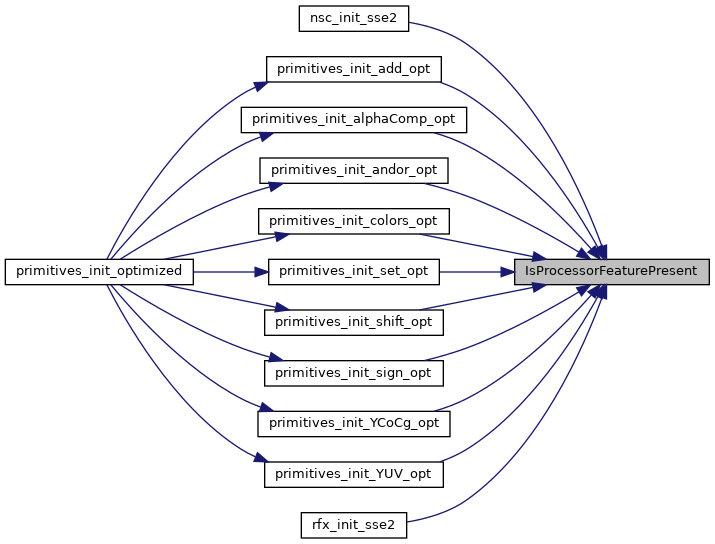

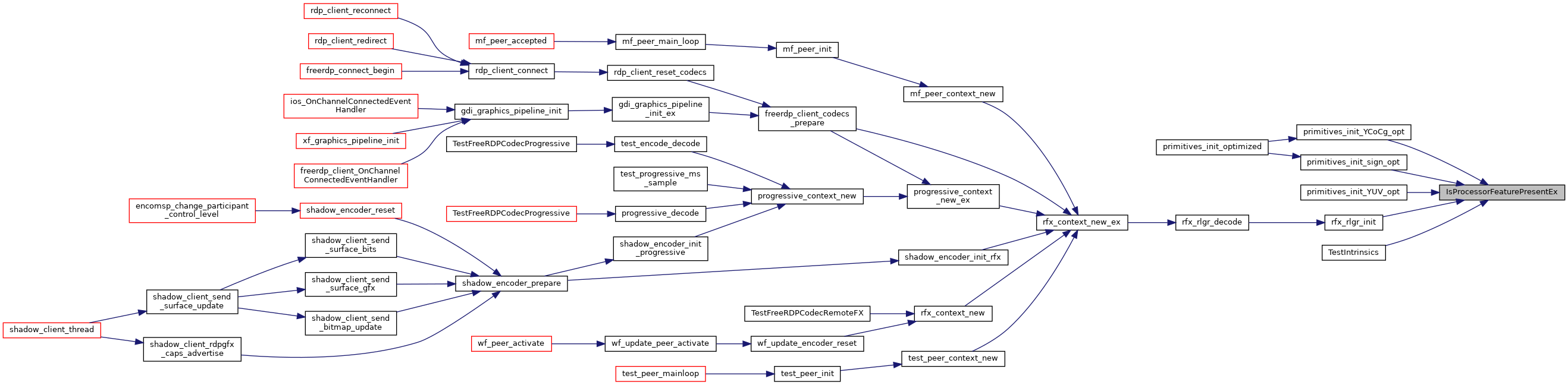

Here is the call graph for this function:

Here is the caller graph for this function:

◆ IsProcessorFeaturePresentEx()

| WINPR_API BOOL IsProcessorFeaturePresentEx | ( | DWORD | ProcessorFeature | ) |

Here is the caller graph for this function:

◆ SetLocalTime()

| WINPR_API BOOL SetLocalTime | ( | CONST SYSTEMTIME * | lpSystemTime | ) |

◆ SetSystemTime()

| WINPR_API BOOL SetSystemTime | ( | CONST SYSTEMTIME * | lpSystemTime | ) |

◆ winpr_GetTickCount64()

| WINPR_API ULONGLONG winpr_GetTickCount64 | ( | void | ) |

Here is the call graph for this function:

◆ winpr_GetTickCount64NS()

| WINPR_API UINT64 winpr_GetTickCount64NS | ( | void | ) |

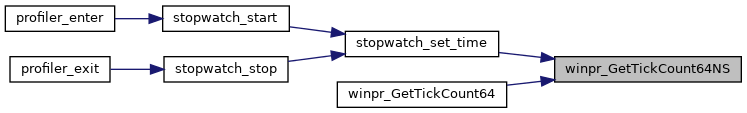

Here is the caller graph for this function:

◆ winpr_GetUnixTimeNS()

| WINPR_API UINT64 winpr_GetUnixTimeNS | ( | void | ) |

Here is the call graph for this function:

Here is the caller graph for this function: